サウジアラビアのキング・アブドラ科学技術大学(KAUST)で行われた研究によって、これまで平面に広げるしかなかった半導体チップを“縦に積み上げる”ことで性能を高める新しい方法が実証されました。

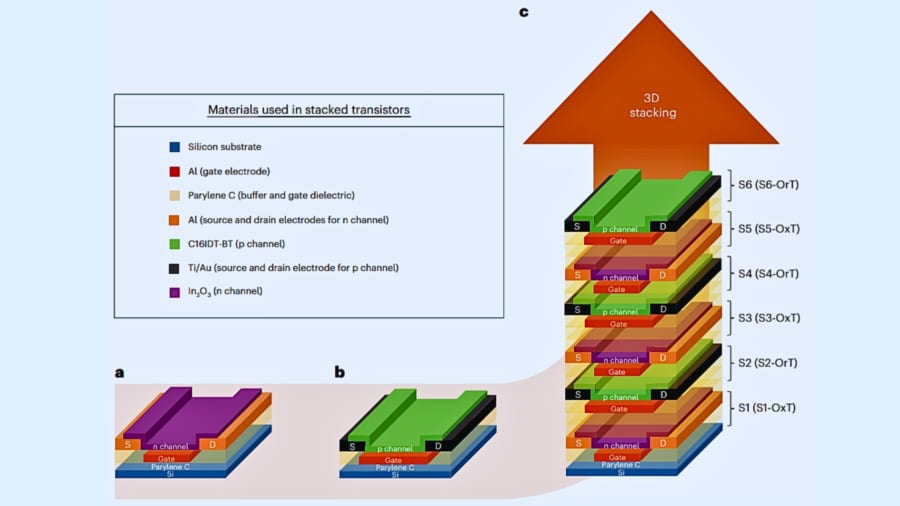

研究チームは、無機材料と有機材料を交互に重ねた6段=41層構造のハイブリッドCMOSチップを開発し、従来2段が限界とされていた積層技術を大きく更新。

600個のトランジスタを評価した結果、入力信号を約95倍に増幅しながら、消費電力をわずか0.47マイクロワットに抑えることに成功しました。

これにより、平面上の微細化(いわゆるムーアの法則)が行き詰まりつつある現在、半導体の進化に“高さ”という新たな方向性が示されたのです。

チップを上に積むというこの発想は、スマートデバイスやウェアラブル機器の設計をどのように変えていくのでしょうか?

研究内容の詳細は2025年10月14日に『Nature Electronics』にて発表されました。

目次

- ムーアの法則が限界へ、突破口は「積層」

- 立体積層チップはいかにして成功したか

- 限界を越える新発想―半導体は『上』へ伸びる

ムーアの法則が限界へ、突破口は「積層」

今や私たちの生活に欠かせないスマートフォンやパソコンの性能は、「トランジスタ」という微細な電子部品がいくつ搭載されているかで大きく決まります。

そのトランジスタの数を「約2年ごとに倍増できる」という夢のような法則が、半導体業界に長年君臨してきた「ムーアの法則」です。

しかし、近年、この「トランジスタをどんどん小さくする」道のりが物理的な限界に近づいてきました。

なぜかというと、トランジスタをあまりにも小さくしすぎると、今まで問題にならなかった量子トンネル効果という現象によって電流が漏れてしまうからです。

これは、本来電気が流れてはいけない場所に電流が勝手に通り抜ける現象で、せっかく細かなトランジスタを作っても性能が下がってしまうのです。

さらに、小型化が進むほど製造装置や手順が極端に複雑になり、コストも急激に高騰するという悪循環が起きています。

つまり、ただ平面的にトランジスタを小さくしていく道だけでは、性能向上が頭打ちになってしまうのです。

こうした問題を背景に、「小型化の限界に近づいた今、これからは平面以外の方向にも目を向けなければならない」という意識が業界全体で高まっています。

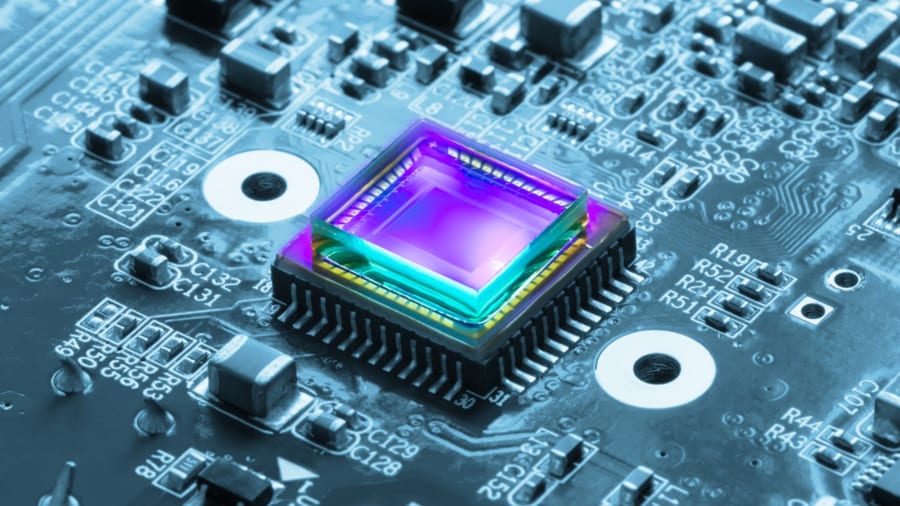

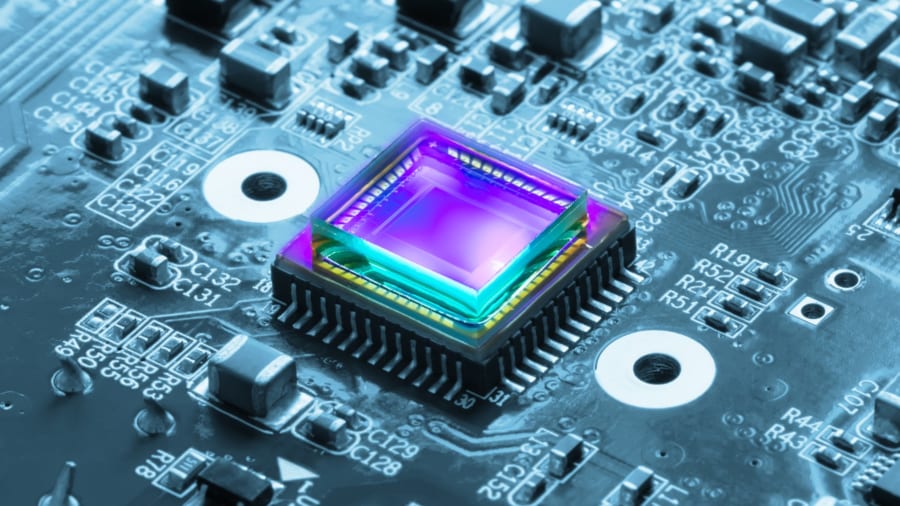

そこで注目されているのが、チップを平面的にではなく縦方向に重ねて積むという新しいアプローチです。

とくに期待されているのが、有機素材と無機素材という異なるタイプの半導体を組み合わせて作るハイブリッドCMOSチップです。

従来の半導体チップは、主にシリコン(ケイ素)という無機材料だけを使って作られてきましたが、ハイブリッドCMOSチップは、シリコンなどの無機材料に、有機材料(プラスチックに近い高性能樹脂)を組み合わせて作るのが特徴です。

この異なる材料の組み合わせは、比較的低い温度で製造できるという利点があり、高温に弱い柔軟な基板や大きな面積の基板でも作りやすいと期待されています。

これにより、従来のシリコンチップでは難しかった、折り曲げ可能な電子回路や身体に貼りつけられるウェアラブルデバイスの実現にも道が開ける可能性があります。

ただし、この縦に積む「3次元集積化」という手法には、まだ大きな課題が残っています。

有機材料と無機材料では、製造温度や加工方法が異なるため、交互に積み重ねる際にうまく適合させるのが難しいのです。

異なる材料を使った層を重ねていくと、接合面がデコボコになったり、熱によるダメージや層同士のズレが蓄積したりする問題が発生します。

いわば、異なる材料でできた繊細な層を何段にも重ねる「多層ケーキ」を作るようなもので、一段ごとの精度が少しでも狂うと全体の出来栄えに影響してしまうのです。

そのため、これまではハイブリッドCMOSの積層構造は実用上せいぜい2段が限界で、それ以上の多層化は難しいとされてきました。

では、もしこの技術的な壁を突破してチップを3段、4段、さらには6段以上も積み重ねることができたら、何が起きるのでしょうか。

横方向の小型化に頼らず、縦方向にトランジスタの数を増やせるとすれば——

それはムーアの法則の限界を超える、新しい進化の道になるかもしれません。

立体積層チップはいかにして成功したか

研究チームは挑戦にあたり、無機と有機という性質のまったく違う2種類の半導体に注目しました。

n型の金属酸化物トランジスタ(電子が動くタイプ)には酸化インジウム(In₂O₃)という無機材料を、p型の有機半導体トランジスタ(正孔が動くタイプ)にはC16IDT-BTという樹脂系の高性能材料を使いました。

この異なる材料を交互に積み重ねることで、ひとつのチップの中に“2つの世界”を共存させることができるのです。

有機はやわらかくて加工しやすく、無機は硬くて丈夫。両者の長所をうまく組み合わせることが狙いでした。

ただし、これを6段も重ねるのは並大抵のことではありません。

最大の敵は「熱」でした。

高温の製造工程を使えば下の層の有機物が焦げてしまう一方、温度を下げすぎると層をしっかり固めることができません。

この難題を解くために研究チームは、製造の多くを室温近くで行い、主要な工程を150℃以下に抑える工夫をしました。

さらに、200℃で短時間の加熱処理を行うことで、トランジスタの開閉特性(SS値)を改善できることもわかりました。

つまり、「焦がさず固める」というギリギリの温度設定を見つけ出したのです。

もちろん、積み重ねにはもうひとつの壁――“ズレ”の問題もありました。

層の表面がわずかに波打つだけでも、上に乗せた層がうまく動かなくなるのです。

研究チームは、各層の表面をナノメートル単位で磨き上げ、層と層の位置を正確に合わせる技術を磨き上げました。

結果として、6層をきれいに積み上げた“電子のタワー”が完成しました。

実際の評価では、測定用の細い針のような電極を使って各層の電気的な性能を調べました。

すると、6層のトランジスタはいずれもおおむね設計どおりに動作し、積層による性能の劣化はわずかであることが確認されました。

下の層ほど安定しており、上に行くほどややばらつきが出ましたが、全体としては良好な結果でした。

この段階で、彼らが積み上げた構造が単なる実験ではなく、実用化に近い設計になりつつあることがわかりました。

そのうえで、チームは600個のトランジスタを使って300個のインバータ回路(入力信号を反転させる基本ユニット)を作成し、その動作を詳しく調べました。

結果は驚くべきもので、6層チップのインバータは入力電圧の約94.84倍を出力に変換できる高い増幅率(ゲイン)を示しました。

しかも消費電力はわずか0.47マイクロワット。

従来の報告では、同じ規模のインバータ回路に約210マイクロワットが必要でした。

比較すると、今回のチップはおよそ450分の1という圧倒的な省エネ性能を実現したことになります。

電気をほとんど使わずに信号を増幅できる――これはまさに「静かに力強いチップ」と言えるでしょう。

この成果の裏には、トランジスタを縦に積み重ねることで配線距離を短くし、電流の流れを効率的にした効果があります。

つまり、“横に広げる”のではなく“上に伸ばす”ことで、チップ全体のエネルギー損失を大きく抑えたのです。

その結果、性能と省エネという、これまで両立が難しかった目標を同時に実現することに成功しました。

この新しいアプローチは、単なる性能アップにとどまりません。

たとえば、曲げられるディスプレイや体に貼るセンサーなど、薄くて広い電子デバイスの内部で、より高密度な頭脳を作る鍵になる可能性があります。

平面の限界を立体的な積層で突破しようというこの試み――その第一歩が、今回の6段チップなのです。

限界を越える新発想―半導体は『上』へ伸びる

「横がダメなら縦がある」——今回の研究が私たちに教えてくれた一番大切なことです。

半導体の世界で何十年も信じられてきたムーアの法則は、そろそろ限界に近づいています。

今回、研究チームが示したのは、この限界に対する別の道を実装で示したということでした。

これまでチップ性能の向上といえば、ひたすらトランジスタを小さくし、平面にびっしりと並べていくことでしたが、それを大胆に「縦方向へ積み重ねる」という発想に切り替えたのです。

この発想の転換によって、チップ内部のトランジスタの数を増やし、配線距離を短くして電気信号の流れをより効率的にすることにも成功しました。

社会的な影響も大きいと考えられます。

たとえば、曲げられるディスプレイや身体に貼る健康モニター、身の回りのものがインターネットにつながるIoT技術など、柔らかくて大きな面積が求められるデバイスに、この成果が追い風になる可能性があります。

こうしたデバイスに「高密度で省エネな電子の頭脳」を直接埋め込めるようになれば、ネットワークに頼らず端末自身が情報処理を行えるようになり、通信の遅延を減らしたり、電池寿命を延ばしたりできるかもしれません。

研究チームも、大型で柔軟な基板上にエネルギー効率の良い電子回路を作るための技術基盤を目指していると述べています。

もちろん、今すぐ何もかもが実現できるわけではありません。

この技術には、まだ「熱への耐性」という大きな課題が残っています。

今回作ったチップは、摂氏50度を超える環境では性能が徐々に下がることが分かりました。

日常生活で使う機器なら問題ないかもしれませんが、産業用途では、もう少し高温でも安定して動作できる必要があります。

熱に弱い有機材料を低温プロセスで積み重ねる技術の宿命とも言えますが、ここをどう改善していくかは今後の重要なテーマです。

それでも、今回の成果がもつ価値は非常に大きいものです。

「平面を諦めて縦に進む」というアイデアが、記録的な規模で実装され、現実的な選択肢として示されたのです。

ムーアの法則という巨大な壁の前で立ち止まっていた半導体業界に、「上に行く」という新しい階段が現れた瞬間と言えるでしょう。

もしかしたら未来のPCパーツ店では、半導体チップが板状ではなく、サイコロのような立方体の形で並んでいるかもしれません。

参考文献

Scientists smash record in stacking semiconductor transistors for large-area electronics

https://www.eurekalert.org/news-releases/1101744

元論文

Three-dimensional integrated hybrid complementary circuits for large-area electronics

https://doi.org/10.1038/s41928-025-01469-0

ライター

川勝康弘: ナゾロジー副編集長。 大学で研究生活を送ること10年と少し。 小説家としての活動履歴あり。 専門は生物学ですが、量子力学・社会学・医学・薬学なども担当します。 日々の記事作成は可能な限り、一次資料たる論文を元にするよう心がけています。 夢は最新科学をまとめて小学生用に本にすること。

編集者

ナゾロジー 編集部